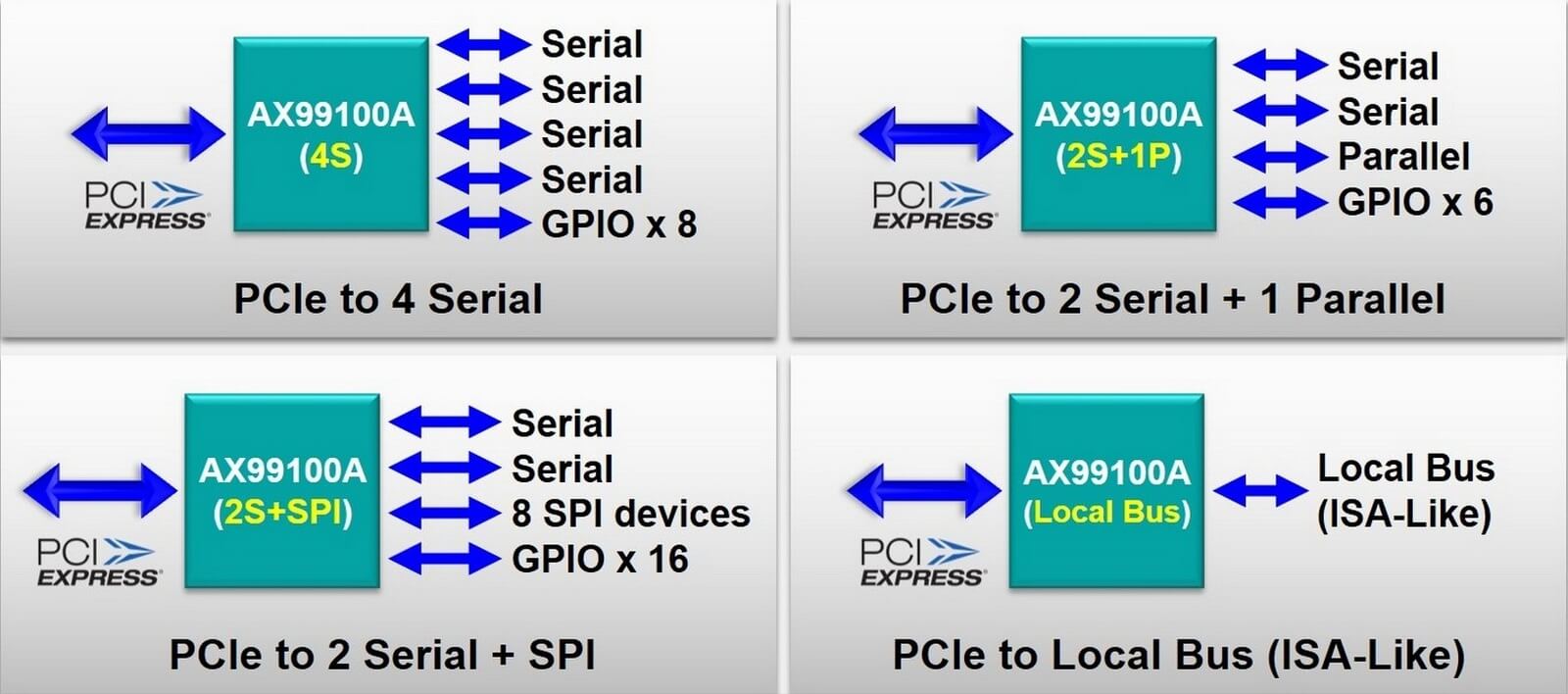

The AX99100A is a PCIe to Multi I/O (4S, 2S+1P, 2S+SPI, LB) Controller that integrates a single-channel (X1) PCIe 2.0 Gen 1 endpoint controller and PHY with a variety of peripherals such as four high-speed serial ports, one parallel port, high-speed SPI master, I2C master, Local Bus (ISA-Like) and 24 GPIOs. AX99100A supports four modes, namely 4S (PCIe to Quad Serial), 2S+1P (PCIe to Dual Serial and Single Parallel), 2S+SPI (PCIe to Dual Serial and SPI), and LB (PCIe to Local Bus/ISA-Like). It is suitable for various I/O interface connectivity applications such as PCIe serial/parallel cards, PCIe data acquisition (DAQ) cards, industrial computers, industrial automation equipment, measurement instrumentation equipment, medical devices, POS terminals and industrial embedded systems.

AX99100A

PCIe to Multi I/O (4S, 2S+1P, 2S+SPI, LB) Controller

Add Favorites

Overview

Features

● A PCIe 2.0 Gen 1 to Multi I/O (4S, 2S+1P, 2S+SPI, LB) Controller with 4S, 2S+1P, 2S+SPI, 2S, 1S, Local Bus, and GPIO support

Target Applications

> PCIe UART/RS‑232/RS‑485 Serial Cards

Diagram

Development Board

AX99100A PCIe to 4S Demo Board (AX99100A-DMB-4S-1)

This is an AX99100A PCIe to 4S adapter for users to evaluate AX99100A PCIe to 4S functionalities.

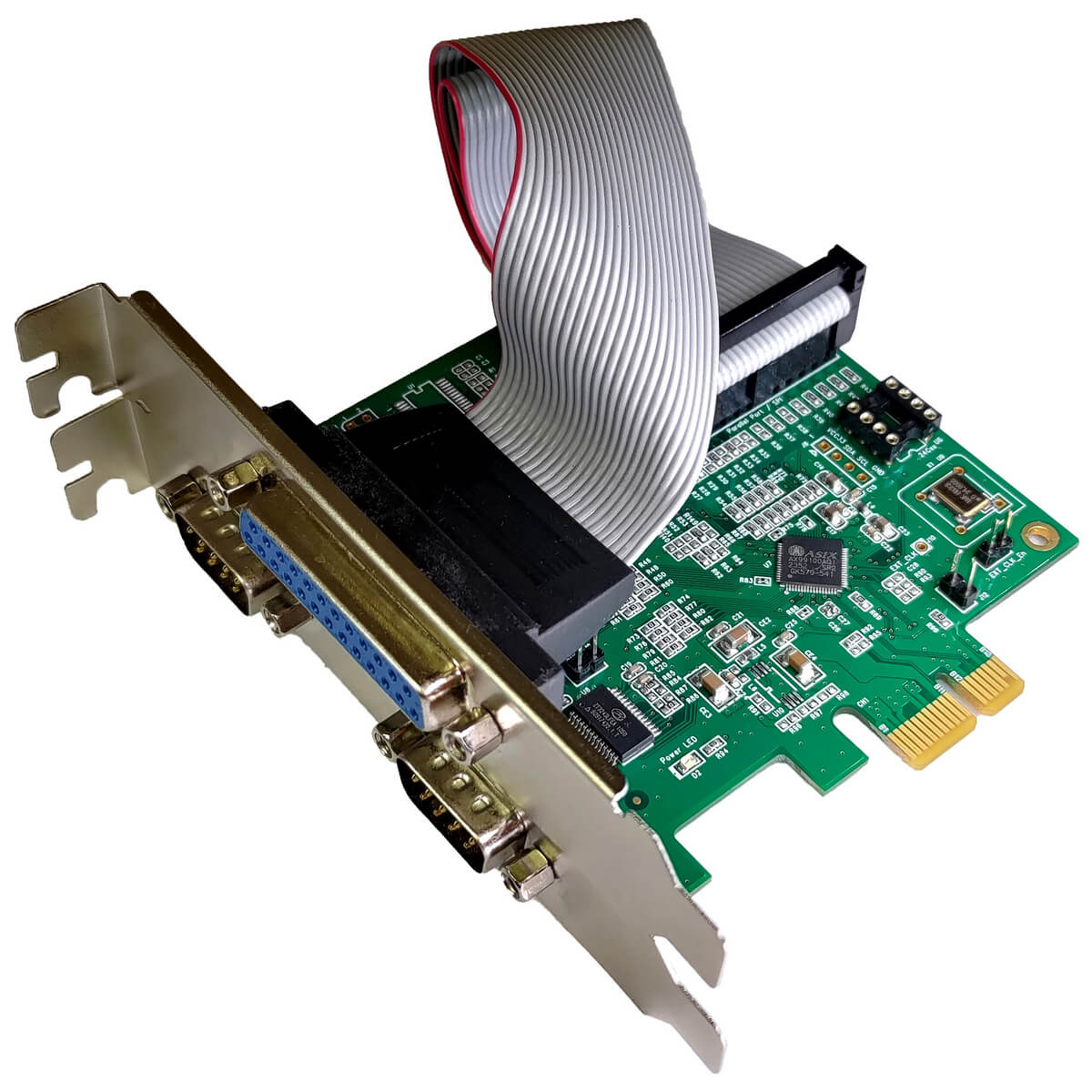

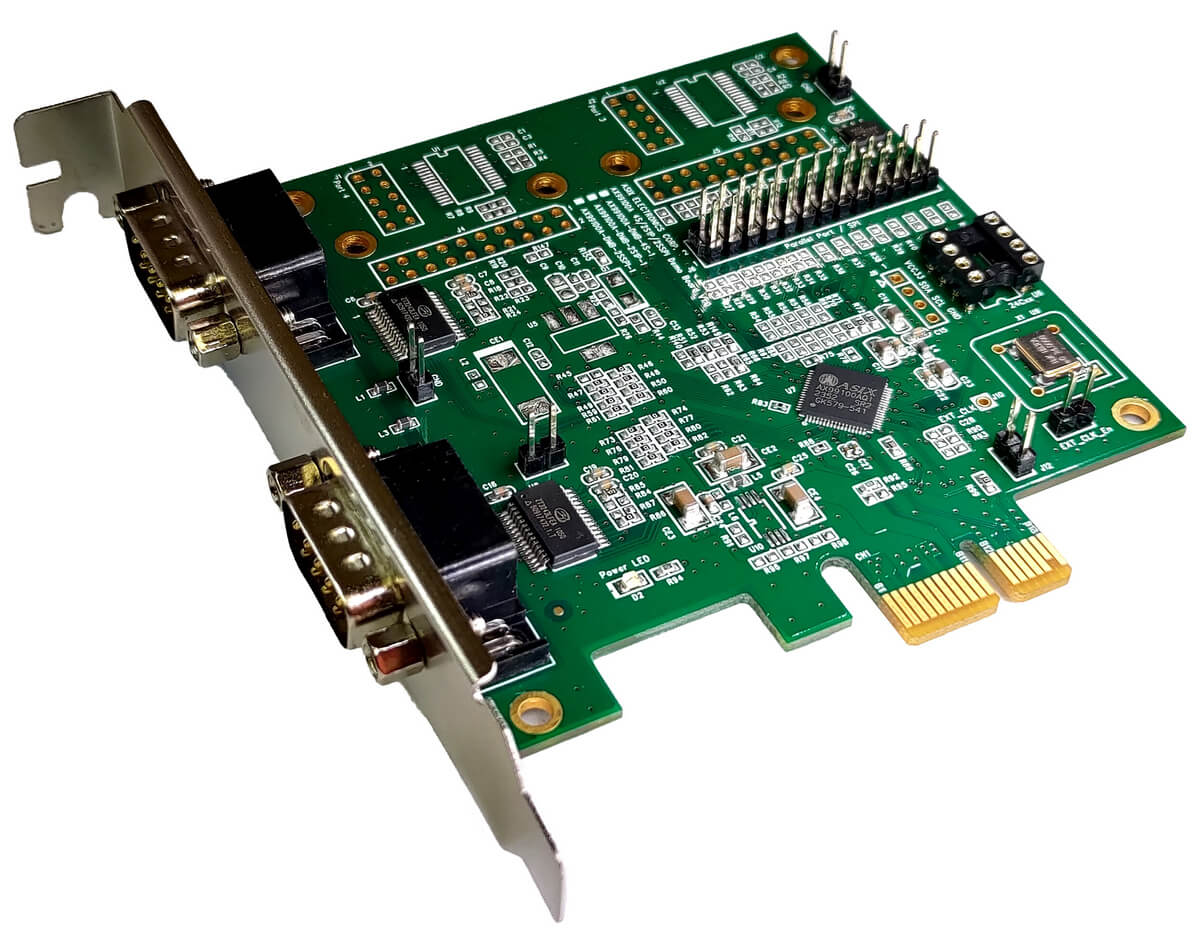

AX99100A PCIe to 2S1P Demo Board (AX99100A-DMB-2S1P-1)

This is an AX99100A PCIe to 2S1P adapter for users to evaluate AX99100A PCIe to 2S1P functionalities.

AX99100A PCIe to 2S1SPI Demo Board (AX99100A-DMB-2SSPI-1)

This is an AX99100A PCIe to 2S1SPI adapter with embedded SPI Flash for users to evaluate AX99100A PCIe to 2S1SPI functionalities.

AX99100A Local Bus Demo Board

This is an AX99100A PCIe to Local Bus + Async. SRAM Module adapter for users to evaluate AX99100A PCIe to Local Bus interface functionalities. Included AX99100A Local Bus Async. SRAM Module Board

Download

Hardware Design Documentation

AX99100A PCIe to 4S Demo Board Reference Schematic

AX99100A PCIe to 2S1P Demo Board Reference Schematic

AX99100A PCIe to 2S1SPI Demo Board Reference Schematic

AX99100A PCIe to Local Bus Demo Board Reference Schematic

AX99100A Local Bus Async SRAM Module Board Reference Schematic

AX99100A PCIe to 4S/2S1P/2S1SPI Demo Boards PCB Layout Files

AX99100A Local Bus Async SRAM Module Board PCB Layout Files

Software & Tools

Windows 11 64-bit Driver

For x64 CPU platform, HLK/WHCK certifiedWindows 10 32-bit Driver

For x86 CPU platform, HLK/WHCK certified