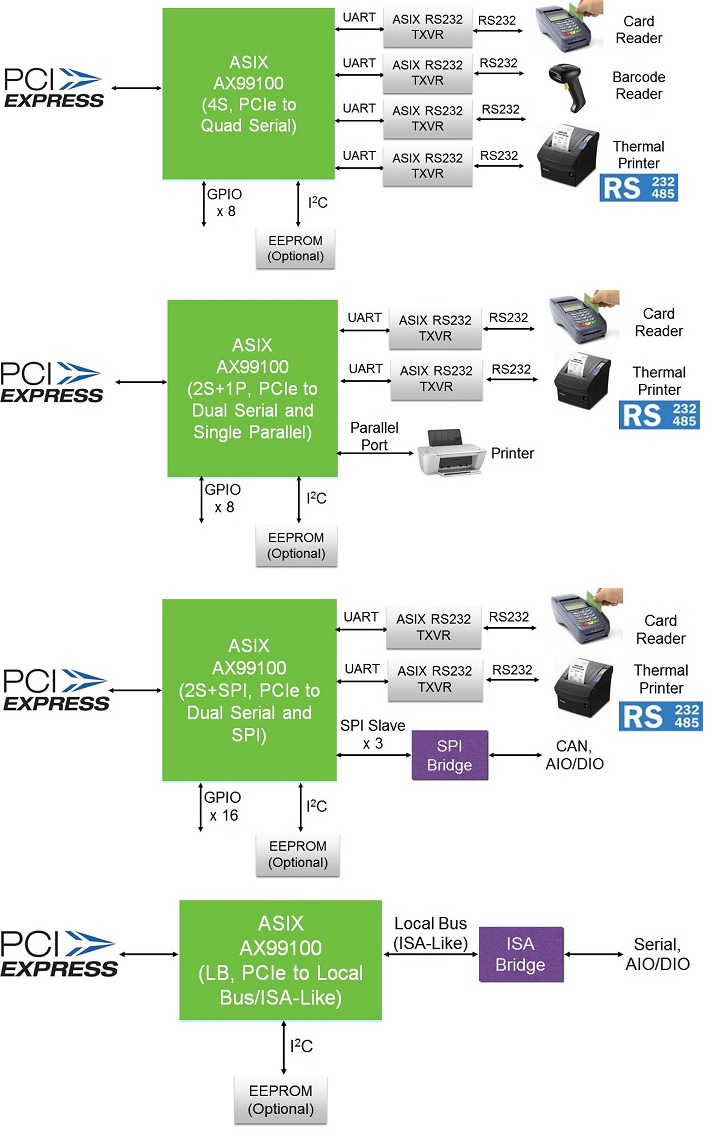

The AX99100 is a single chip solution that fully integrates PCIe 2.0 Gen 1 end-point controller and SerDes with a variety of peripherals such as four High Speed Serial Ports, one Parallel Port, I²C Master, High Speed SPI, Local Bus (ISA-Like) , and GPIOs. It consists of four main configurations such as 4S (PCIe to Quad Serial), 2S+1P (PCIe to Dual Serial and Single Parallel), 2S+SPI (PCIe to Dual Serial and SPI), and LB (PCIe to Local Bus/ISA-Like) for different kinds of applications.

AX99100

PCIe to Multi I/O (4S, 2S+1P, 2S+SPI, LB) Controller

Add Favorites

Overview

Features

● PCI Express

-- Single-lane (X1) PCI Express End-point Controller with PHY integrated

-- Compliant with PCI Express 2.0 Gen 1

-- Compliant with PCI Express card specifications

-- Compliant with PCI Power Management 1.2

-- Supports four PCI Express functions

-- Supports both legacy and MSI Interrupt

-- Supports ASPM Power Management

● Serial Port Interface

-- Dual or Quad UARTs

-- Supports RS-232/RS-422/RS-485 multiprotocol

-- Bi-directional speeds up to 25 Mbps per port

-- Full Serial Modem Control

-- Supports Hardware, Software Flow Control

-- Supports 5, 6, 7, 8 and 9-bit Serial format

-- Supports Even, Odd, None, Space and Mark parity

-- Supports Custom baud rate by internal PLL or external clock

-- Supports On Chip 256 Byte depth FIFOs in Transmit, Receive path of each Serial Port

-- Supports remote wakeup and power management features

-- Serial Port transceiver shutdown support

-- Supports Slow IrDA mode (up to 115200bps) on all Serial Ports

-- Supports multi-drop application for 9-bit mode

-- Supports DMA burst transfer

● Parallel Port

-- Compatible with IEEE 1284 – SPP/Byte/ECP Mode

● SPI Interface

-- Programmable SPI clock frequency up to 42MHz

-- Supports Mode 0, Mode 1, Mode 2 and Mode 3 timing modes

-- Supports MSB/LSB first transfer fashion

-- Programmable peripheral chip select, selecting up to 7 SPI devices

-- Supports Non-Burst-Type transfer up to 8 bytes and/or Burst-Type transfer via DMA mode for high performance

-- Supports to fragment large data block into several smaller transfers on SPI bus to reduce software loading

-- Supports programmable transfer 0 ~ 8 bytes OP-Code field in each transfer automatically to reduce software loading

-- Supports wake-up by SWAKEn pin from Slave

● Local Bus Interface

-- Supports memory or I/O access through PCIe BAR0/1 to local bus interface, each BAR mapping to local bus\' chip select (CS0n and CS1n)

-- Supports direct access and bus master access (auto-increment and fixed address)

-- Supports 8-bit or 16-bit data bus width (little and big endian bus swap)

-- Supports up to 2 Kbytes address space and 2 chip select outputs when separated address/data bus style

-- Supports up to 64 Kbytes address space and 2 chip select outputs when multiplexed address/data bus style

-- Supports programmable local chip select region

-- Supports “Slave Request based DMA” access for interfacing with external device with bus master

-- Supports clock out, CLKO, up to 62.5MHz

-- Supports asynchronous or synchronous Local Bus with required clock output, CLKO

-- Supports programmable bus access cycles, self-terminated bus access cycles and back-to-back turnaround cycles

-- Supports programmable RSTO, ALE, RDY, DREQ0/1, DACK0/1, CLKO polarity, and INT0/1 level/edge trigger

-- Supports wake-up by INT0/1 and DREQ0/1 pins

● Supports I2C Master Interface

● Up to 24 bi-directional GPIO lines including 8 dedicated GPIO and 16 multi-function GPIO

● Integrates on-chip power-on reset circuit

● On Chip 3.3 to 1.2V Regulator

● 68-pin QFN RoHS compliant package

● Operating temperature range: -40 to +85°C

Diagram

Development Board

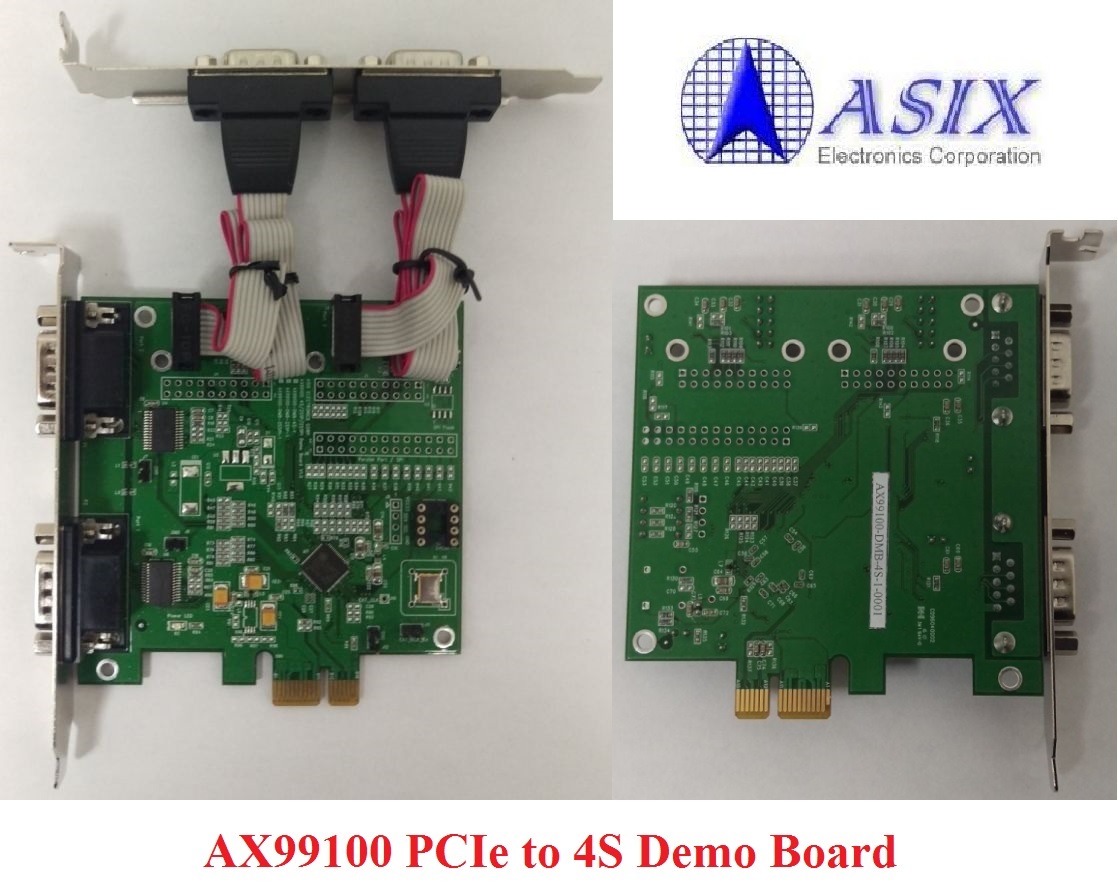

AX99100 PCIe to 4S Demo Board (AX99100-DMB-4S-1)

This is an AX99100 PCIe to 4S adapter for users to evaluate AX99100 PCIe to 4S functionalities.

AX99100 PCIe to 2S1P Demo Board (AX99100-DMB-2S1P-1)

This is an AX99100 PCIe to 2S1P adapter for users to evaluate AX99100 PCIe to 2S1P functionalities.

AX99100 PCIe to 2S1SPI Demo Board (AX99100-DMB-2SSPI-1)

This is an AX99100 PCIe to 2S1SPI adapter with embedded SPI Flash for users to evaluate AX99100 PCIe to 2S1SPI functionalities.

AX99100 Local Bus Demo Board

This is an AX99100 PCIe to Local Bus + Async. SRAM Module adapter for users to evaluate AX99100 PCIe to Local Bus interface functionalities.

Included AX99100 Local Bus Async. SRAM Module Board

FAQs

Hardware Design Considerations

-

Where can I obtain the latest AX99100 datasheet, reference schematic and other hardware design archives?

Please register MyASIX membership and then download the latest AX99100 datasheet, reference schematic, PCB layout guide, etc. from AX99100 Product web page directly.

-

Can ASIX help me to review my own AX99100 schematic and PCB layout?

Yes, please deliver your own AX99100 schematic and PCB layout files to ASIX’s Support (support@asix.com.tw) for further review before making your own AX99100 PCB board.

-

Is the I2C EEPROM required for AX99100 serial/parallel/SPI applications?

The I2C EEPROM is optional for some of AX99100 serial/parallel/SPI applications.

-

Is the I2C EEPROM required for AX99100 Local Bus/ISA-Like applications?

Yes, the I2C EEPROM is required for AX99100 Local Bus/ISA-Like applications. Please contact ASIX Sales (Sales@asix.com.tw) to further support.

-

How to program AX99100 I2C EEPROM in-circuit?

The AX99100 supports a Windows EEPROM Utility to program the I2C EEPROM in-circuit.

-

Can AX99100 support full ISA interface?

No, AX99100 only supports 10-bit address bus (A[9:0]) for ISA-Like applications so AX99100 does not support full ISA interface (with 24-bit address bus). Please contact ASIX Sales (Sales@asix.com.tw) to further support.

-

Does ASIX support RS-232/RS-485 transceivers solutions?

Yes, ASIX also supports different RS-232/RS-485 transceivers solutions. Please visit ASIX UART Transceivers/EL Drivers Products Web page for more details.

Software Design Considerations

-

Where can I obtain the latest AX99100 PCIe to Serial/Parallel drivers?

Please visit AX99100 Driver Download web pages to download proper drivers for typical AX99100 PCIe to Serial/Parallel target applications.

-

Where can I obtain AX99100 PCIe to Local Bus/ISA-Like/SPI drivers and demo tools?

For AX99100 PCIe to Local Bus/ISA-Like/SPI applications, ASIX provides AX99100 PCIe to Local Bus/SPI Windows/Linux drivers and demo tools for customers to evaluate the basic functionalities of AX99100 PCIe to Local Bus + Async SRAM Demo Board and AX99100 PCIe to SPI demo board. ASIX can also provide the source codes for customers’ reference if necessary. Please contact ASIX Sales (Sales@asix.com.tw) for further support.

-

How to change the COM port number of AX99100?

Yes, we can change the COM port number by using a drop down list located in AX99100 Windows COM Port Properties. To change the COM port number, go to "COM Port Properties => Port Settings => Change Port Number => COM Port Number".

-

How to change the LPT port number of AX99100?

Yes, we can change the LPT port number by using a drop down list located in AX99100 Windows LPT Port Properties. To change the LPT port number, go to "LPT Port Properties => Port Settings => LPT Port Number".

-

Is it possible to manually change the IRQ of AX99100 Parallel/Serial ports?

It is not possible to manually change IRQ setting of all PCIe devices in any operating systems because the IRQ used by the device is assigned by the PCIe system and cannot be changed. Usually the only way to change the IRQ of a PCIe device is to move it to a different PCIe slot. Each slot is usually assigned a different IRQ, although this is not always true. Each system may handle the assignment of IRQs differently.

-

Is it possible to remap the I/O addresses of AX99100 Parallel/Serial ports to Legacy I/O address values?

In order to be compatible with some legacy software, some users might need to remap the assigned I/O addresses of AX99100 Parallel/Serial ports to Legacy (ISA type) I/O address (such as 378h, 3F8h, etc.). It is possible on DOS and Windows 95/98/ME operating systems but impossible on Windows NT/2000/XP/Vista/7/8 operating systems because the Remap I/O Address feature is only supported on DOS and Windows 95/98/ME operating systems but is not supported on Windows NT/2000/XP/Vista/7/8.x/10 operating systems. As the newer Windows systems maintain a much tighter control over the I/O devices and prevent any Re-Mapping I/O Address operation at device driver level. When the Re-Mapping I/O Address is not permitted, the device must use the I/O Addresses assigned by the PCIe system at Boot-Up. If the software application expects the Parallel/Serial ports to use Legacy I/O address resources, it will not be possible to make it work with the Parallel/Serial ports of PCIe based devices on Windows NT/2000/XP/Vista/7/8.x/10 platforms. On DOS platform, AX99100 can remap the I/O addresses of the Parallel/Serial ports to desired values by running AX99100 DOS utility. However, on Windows 95/98/ME platforms, you can only remap the I/O addresses of the Serial ports (but not Parallel port).

Download

Hardware Design Documentation

AX99100 PCIe to 4S Demo Board Reference Schematic

AX99100 PCIe to 2S1P Demo Board Reference Schematic

AX99100 PCIe to 2S1SPI Demo Board Reference Schematic

AX99100 PCIe to Local Bus Demo Board Reference Schematic

AX99100 Local Bus Async SRAM Module Board Reference Schematic

AX99100 PCIe to 4S/2S1P/2S1SPI Demo Boards PCB Layout Files

Software & Tools

Linux kernel 6.x/5.x/4.x/3.x/2.6.x Driver

For all Android systems, Linux kernel 2.6.14 and laterWindows 11 64-bit Driver

For x64 CPU platform, HLK/WHCK certifiedWindows 10 32-bit Driver

For x86 CPU platform, HLK/WHCK certifiedWindows 10 64-bit Driver

For x64 CPU platform, HLK/WHCK certifiedWindows 8.x 32-bit Driver

For x86 CPU platform, HLK/WHCK certifiedWindows 8.x 64-bit Driver

For x64 CPU platform, HLK/WHCK certifiedWindows 7/Vista/XP 32-bit Driver

For x86 CPU platform, WHCK certifiedWindows 7/Vista/XP 64-bit Driver

For x64 CPU platform, WHCK certified