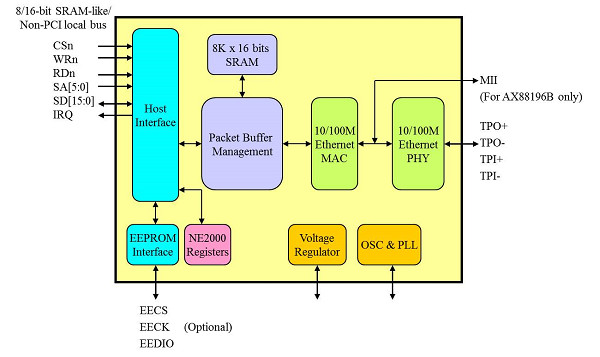

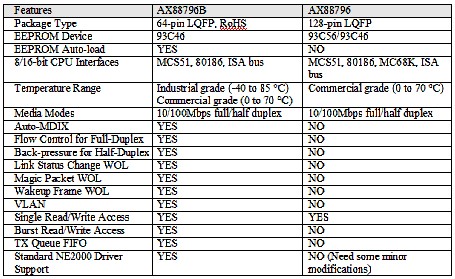

● High-performance non-PCI local bus

-- Supports both 8 bit and 16 bit local CPU interfaces include MCS-51 series, 80186 series CPU and ISA bus

-- SRAM-like host interface (US Patent Approval), easily interfaced to most common embedded MCUs

-- Embeds 8Kx16 bits SRAM for packet buffers

-- Supports Slave-DMA to minimize CPU overhead

-- Supports burst-mode read for highest performance applications

-- Interrupt pin with programmable Hold-off timer

● Single-chip Fast Ethernet controller

-- Compatible with IEEE802.3, 802.3u standards

-- Integrates Fast Ethernet MAC/PHY transceiver in one chip

-- Supports 10Mbps and 100Mbps data rate

-- Supports full and half duplex operations

-- Supports 10/100Mbps N-way Auto-negotiation operation

-- Supports twisted pair crossover detection and auto-correction (Auto-MDIX)

-- Supports IEEE 802.3x flow control for full-duplex operation

-- Supports back-pressure flow control for half-duplex operation

● Supports Wake-on-LAN function to reduce power by following events

-- Detection of a change in the network link state

-- Receipt of a Magic Packet

-- Receipt of a MS wakeup frame

● NE2000 register level compatible instruction

-- Detection performance can be enhanced with only a minor host driver modification from original NE2000 driver

● Supports EEPROM interface to store MAC address(Opitional)

● Supports up to 2 (out) /1 (in/out) General Purpose pins

● Supports LED pins for various network activity indications

● Integrates on-chip 3.3V to 1.8V voltage regulator and require single power supply of 3.3V only

● Integrates on-chip oscillator and PLL. Require only one 25MHz crystal to operate

● 64-pin LQFP , RoHS package

● Operate over 0 to +70 °C or -40 to +85 °C temperature range